汽车芯片和商用级芯片的ESD资格认证

这篇将讨论用于标准商业应用和汽车应用的集成电路的 ESD 资格要求之间的差异。汽车一直都有电路。甚至在电动车头灯和电动启动器出现之前,磁电机就可以提供电脉冲来为火花塞提供动力。多年来,电路的数量稳步增加,今天,收音机早已被取代,成为车辆中最复杂的电子设备。汽车中高科技电子含量的快速增长吸引了电子行业更广泛领域的兴趣,比过去更广泛。希望成为汽车行业供应商的集成电路供应商必须熟悉汽车电子的资质要求。

汽车电子产品的工作环境比大多数消费类应用的工作环境要严酷得多。汽车电子设备必须在明尼苏达州的严冬和夏季穿越死亡谷时正常工作。汽车环境也是一个电噪声环境,线束承载传感电路以及高电流脉冲来操作各种电机和配件。汽车电子产品通常也对安全至关重要。因此,汽车行业对电子元件有自己的一套资格要求也就不足为奇了。(注:在这篇文章中,我试图总结商用和汽车集成电路 ESD 认证之间的差异。本摘要不应作为替代对完整标准的内容来读取。)

1,资质文件

大多数商用集成电路的资格要求由 JEDEC 的 JESD47“集成电路的应力测试驱动资格”[1] 规定,而汽车集成电路则由 AEC(汽车电子委员会)Q100 标准“基于应力的失效机制”规定。《集成电路测试资格》[2]。这两份文件的目的和方法非常相似。这两个文件包括以下类型的要求。

资格所需的压力测试列表,例如:

高温使用寿命

早期故障率

温度湿度偏差

人体模型 (HBM)

带电器件模型 (CDM)

...

每个测试所使用的测试方法的规范

JEDEC:主要是 JEDEC 测试,但也有一些军事测试

AEC:AEC 特定测试以及 JEDEC 和军事测试的组合

每个测试的要求规范,例如:

测试温度

试验时湿度

样本量

允许的不合格样品数量

失败标准

...

当需要进行每项测试时,例如:

设计变更

栅氧化层的变化

金属化的改变

新制造基地

...

2, 静电放电要求

我们现在可以比较 JEDEC 和 AEC 资格文件中的 ESD 测试要求。为此,将在此处复制两个文档中 HBM 和 CDM 的表条目,从而从 AEC 表中删除与当前讨论不相关的两列。

JEDEC (联合电子设备工程委员会)

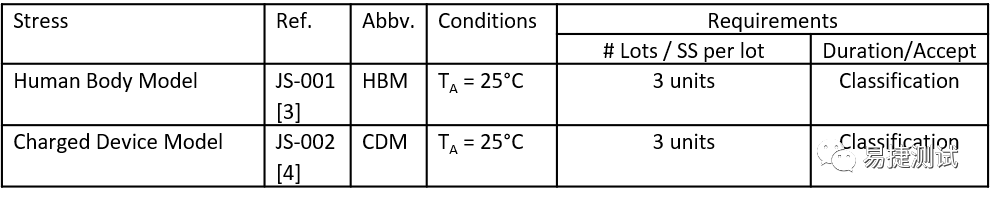

表 1 JESD47K 中 HBM 和 CDM 的 JEDEC 要求

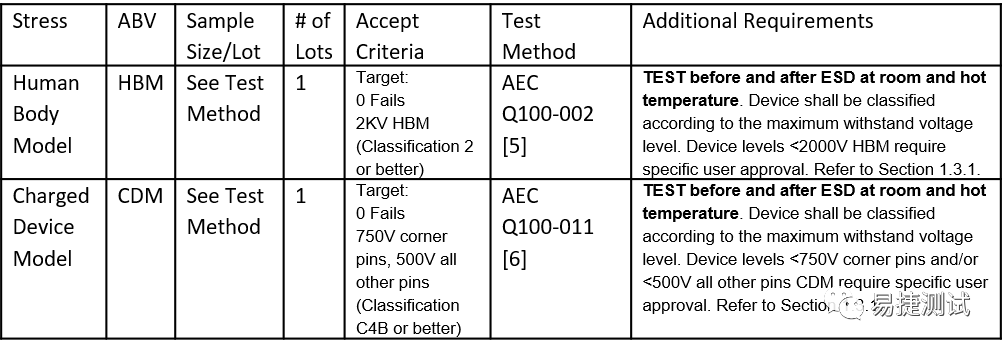

表2 Q100H中HBM和CDM的AEC要求

两种方法的资格要求之间存在三个显著差异。

JEDEC 和 AEC 对于 HBM 和 CDM 的测试标准有所不同

要求不同:JEDEC 要求“分类”,AEC 为 HBM 和 CDM 提供具体目标级别

JEDEC 要求 3 个样品,而 AEC 则说“参见测试方法”

测试标准的差异并不像看起来那么明显。HBM的AEC Q100-002 和 CDM 的 Q100-011 的开头分别有以下声明。

对符合AEC Q100资格的集成电路器件进行的所有HBM测试均应符合 ANSI/ESDA/JEDEC JS-001 规范的最新版本,并具有此处定义的附加要求。

在符合 AEC Q100 要求的集成电路器件上执行的所有 CDM ESD 测试均应符合最新版本的 ANSI/ESDA/JEDEC JS-002 规范,并具有以下说明和要求。

这些声明表明,JEDEC 和 AEC 之间的 HBM 和 CDM 基本测试本质上是相同的。所需的样本数量也相同。JESD47 指定了三个样本,而 JS-001 也指定了三个样本。HBM的 Q100-002 未指定样本数量,因此 AEC 要求受 JS-001 要求的三个样本管辖。对于 CDM,Q100-011 指定了三个样本。

要求的差异更为显著。JEDEC 将要求列为“分类”。因此,要求所有集成电路设计都必须针对 HBM 和 CDM 进行测试。实际要求由集成电路制造商和购买者之间协议确定。多年来,“众所周知”HBM 的规格为2000V,并且由于工业委员会针对ESD目标的活动,该要求已降至1000V。事实上,这种“常识”从来都不是真的,对于商业产品,HBM 和 CDM 的 ESD 级别始终是供应商和购买者之间的协议。

AEC对HBM和CDM的要求要严格得多。AEC ESD 的基本基准是 HBM 通过级别为 2000 V,CMD 通过级别为角引脚 750 V,所有其他引脚为 500 V。从表 2 可以看出,也有例外。用户可以接受较低水平的 ESD 稳健性。第 1.3.1 节的注释是报告的要求,内容如下:

对于 ESD,强烈建议在供应商数据表中指定通过电压,并对任何引脚异常添加脚注。这将允许供应商声明“符合 ESD 2 级 AEC-Q100 标准”。

JEDEC 和 AEC ESD 要求之间的大部分剩余差异在于 Q100-002(针对 HBM)和 Q100-011(针对 CDM)的附加要求。

2.1 人体模型

本节将总结根据 Q100-002 对 HBM 测试的附加要求。

2.1.1 波形要求(Q100-002 第 1.1 节)

这就要求所有测试仪满足所有测试级别的波形要求。(JS-001 中的传统措辞可以解释为测试仪不需要满足所有波形要求,但这绝不是其意图。)

2.1.2 测试夹具板资格(Q100-002 第 2 部分)

要求测试夹具板在所有测试电压(而非限制电压)下满足波形要求。如果电路板被修复,还指定重新鉴定。

2.1.3 器件应力(Q100-002 第 3 节)

要求在 500 V、1000 V 和 2000 V 下对器件施加应力。不得跳过各个级别。JS-001 允许在单一级别进行测试以确定免疫级别。Q100-002还规定,如果设备在500 V电压下失败,则需要在250 V电压下进行测试,如果在125 V电压下测试失败,如果测试仪能够满足波形。

2.1.4 6 引脚或更少的器件(Q100-002 第 4.1 节)

具有 6 个或更少引脚的设备必须使用所有引脚对组合进行测试。(端子 A 上有一个引脚,端子 B 上有一个引脚。)JS-001 要求使用所有引脚组合测试分立器件,并允许使用所有引脚对组合测试具有 10 个或更少引脚的器件。

2.1.5 引脚组合表(Q100-002 4.2 节)

JS-001 包括两种引脚组合选项。表 2B 是 JS-001 原始版本的传统引脚组合,与 JEDEC 和 ESDA 现已废弃的 HBM 标准中的引脚组合相同。表 2A 是一个新表,可减少集成电路上的应力,但需要更多地了解被测器件。表 2A 的目的是减少测试时间,并且可能更重要的是减少由于磨损而导致的故障。Q100-002 要求所有测试都开始使用表 2B。

Q100-002 要求使用表 2B,但给出了可以使用表 2A 的三个选项。

正在使用低寄生测试仪

如果使用表 2B 的故障被视为假故障

如果使用表2B导致因累积应力磨损而失效

2.1.6 低寄生测试仪(Q100-002 第 4.3 节)

如果使用低寄生测试仪(例如两针测试仪),Q100-002 有特殊说明。

必须验证每个压力的连接性

非供应到非供应压力可以使用表 2A 来完成

所有相邻的非电源引脚必须相互承受压力

可以使用 JS-001 第 6.6 节中针对低寄生 HBM 测试仪的选项。

2.1.7 报告(Q100-002 第 5.0 节)

Q100-002 有一个关于报告的部分,这是 JS-001 中所缺少的。除了报告基本测试结果之外,报告部分还需要有关所用测试仪类型的信息、样品的详细信息和测试细节,例如引脚分组、应力电压水平、多个器件上的任何应力分配、应力引脚组合以及任何所执行测试的例外情况。

2.2 清洁发展机制

本节将描述根据 Q100-011 进行 CDM 测试的附加测试要求

2.2.1 测试的应力水平(Q100-011 第 2.3 和 2.5 节)

250 V 是必需的测试级别,如果要报告更高的耐受级别,则必须以 250 V 增量进行测试,直至达到最高通过级别。不允许跳过压力级别。如果设备在 250 V 下出现故障,则应在 125 V 下进行测试,如果在该级别发生故障,则应使用较低的级别,例如 100 V 和 50 V。JS-002 允许在单一电压下进行测试,如果满足所有要求,则该级别可以用作设备 CDM 耐受级别。

2.2.2 排放要求(Q100-011 第 2.5 节)

JS-002 和 Q100-011 之间最显著的差异之一是每个电压和极性的每个引脚的 zap 数量。Q100-011 要求每个电压和极性的每个引脚上有 3 次应力,而 JS-002 要求每个电压和极性“至少 1 次放电”。JS-002 中添加了“至少 1 次放电”的措辞,以便一组测试可以涵盖 JS-002 和 AEC Q100-11 测试。

2.2.3 corner pin 分类(Q100-11 第 1.3.1 和 2.6 节)

AEC CDM 的一个独特功能是角引脚要求。如第 2 节中所述,CDM 的标准鉴定级别为 500 V,角引脚电压为 750 V。AEC Q100-111.中的3.1 节描述了角引脚的定义,而第 2.7 节描述了确定 750 V 电压的两种方法。角引脚分类。

2.2.4 小封装注意事项(Q100-11 第 2.7 节)

Q100-11的这一部分讨论了小封装的CDM测试的困难,并指出在某些情况下可能需要跳过测试,但必须注意这一点并在与用户同意的情况下进行。本节在 JS-002 之前发布,其中包括消除对具有已知 CDM 稳健性历史的技术系列中的小型设备进行进一步 CDM 测试的规定。

2.2.5 晶圆或裸芯片注意事项(Q100-11 第 2.8 节)

本节讨论以晶圆级或裸芯片形式发货的产品的 CDM 测试。该文件允许裸芯片产品在替代封装中进行测试,只要所使用的封装有记录即可。

2.2.6 失效准则(Q100-11 第 2.9 节)

本节将失败定义为不满足所有设备规格。本节还指出,在 CDM 测试之后,设备参数可能会从超出规格范围漂移回规格范围内。本节鼓励在施加压力后立即进行压力后测试,但没有给出时间限制。

2.2.7 验收标准(Q100-11 第 2.10 节)

本节要求,要通过指定的分类级别,设备还必须通过所有较低的测试级别。

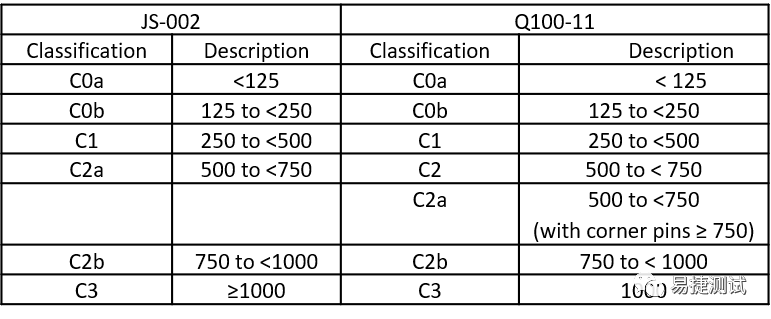

JS-002 和 Q100-11 之间的分类级别也有一些细微的差别。为了满足 750 V 角引脚要求,AEC 在其分类方案中插入了额外的级别,从而造成了一些混乱。新的Q100-11级别C2与JS-002级别C2a的定义相同。为了在 Q100-11 中获得 C2a 电平,需要角引脚电压达到 750 V 或更高。

3,总结

总之,商用与汽车认证的 ESD 要求非常相似。两者都需要基于相同的两个测试标准(HBM JS-001 和 CDM JS-002)进行 HBM 和 CDM 测试。汽车资格认证有额外的要求,包括指定的资格目标水平、CDM 的 3 比 1 zap 以及许多附加要求。好消息是,如果产品满足 AEC Q100 对 ESD 资格的要求,则该产品将远远满足 JEDEC/ESDA 对 ESD 资格的要求。

4,参考文献

[1] JESD47,“集成电路的压力测试驱动资格”,JEDEC 固态技术协会, https://www.jedec.org/。

[2] AEC – Q100 – Rev-H,“基于故障机制的集成电路压力测试资格”汽车电子委员会, http://www.aecouncil.com/。

[3] ANSI/ESDA/JEDEC JS-001-2017,“静电放电灵敏度测试,人体模型 (HBM) – 组件级”,EOS/ESD 协会, https://www.esda.org/和 JEDEC 固态技术协会, https://www.jedec.org/。

[4] ANSI/ESDA/JEDEC JS-002-2018,“静电放电灵敏度测试,充电器件模型 (CDM) – 器件级”,EOS/ESD 协会, https://www.esda.org/和 JEDEC 固态技术协会, https://www.jedec.org/。

[5] AEC–Q100-002 REV-E,“人体模型静电放电测试”,汽车电子委员会, http://www.aecouncil.com/。

[6] AEC-Q100-011 Rev-D,“充电器件模型 (CDM) 静电放电 (ESD) 测试”,汽车电子委员会, http://www.aecouncil.com/