方案简介

描述:

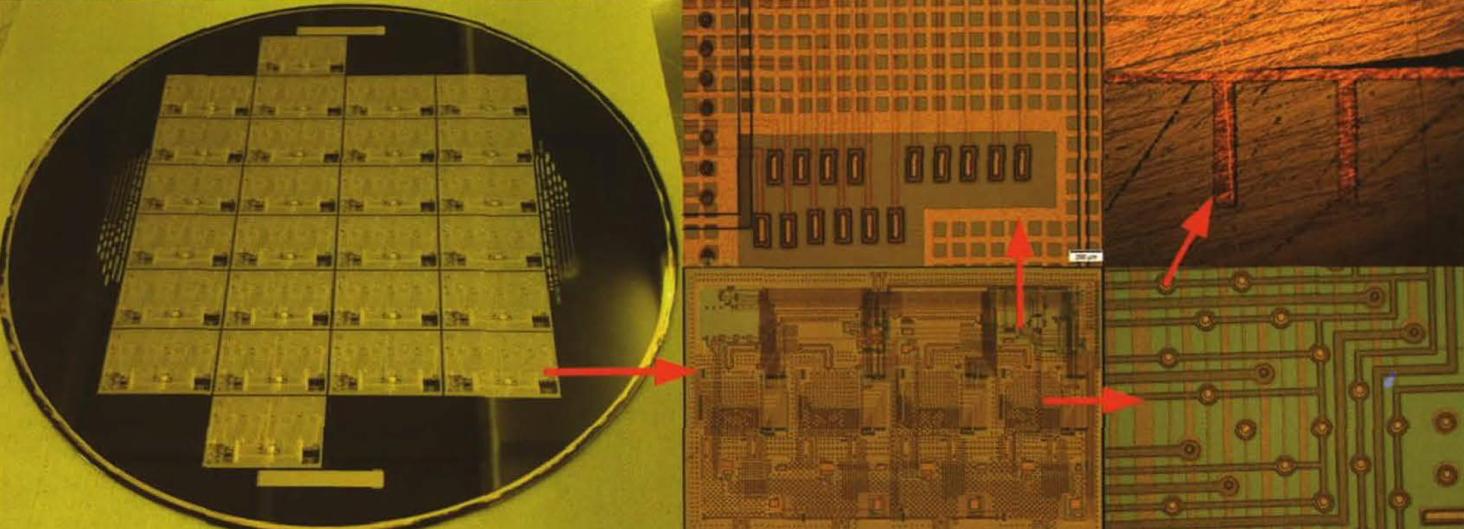

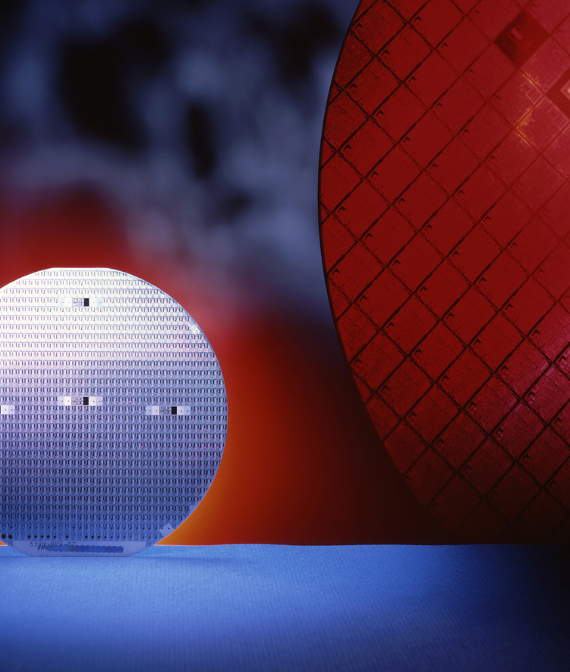

伴随芯片级的三维异构集成芯片的发展,扇出型封装的成熟促进了RDL的发展,因此RDL层的电学特性测试慢慢的将引起人们的重视。由于RDL是将原来设计的芯片线路接点位置(Pad)通过晶圆级金属布线制程和凸块制程得以改变,使芯片能适用于不同的封装形式,所以测试其电学性能的时候需要面对种种难于一般wafer测试的问题。如:芯片薄易碎、测试点分布在wafer的两面且位置不固定、测试设备需要快速且高精度移动、扎点尺寸及力度要可控等。

易捷可提供晶圆级三维异构芯片RDL层双面探针台,最高可实现100points/sec的测试速率,每一面可搭载1组或多组异步机械手臂,通过高灵敏度传感器配合智能的AOI算法可实现扎点力度可控、不破片、不裂片的高精度测试。目前此方案已得到国内三维异构芯片生产厂家认可。

异构芯片中RDL示意图

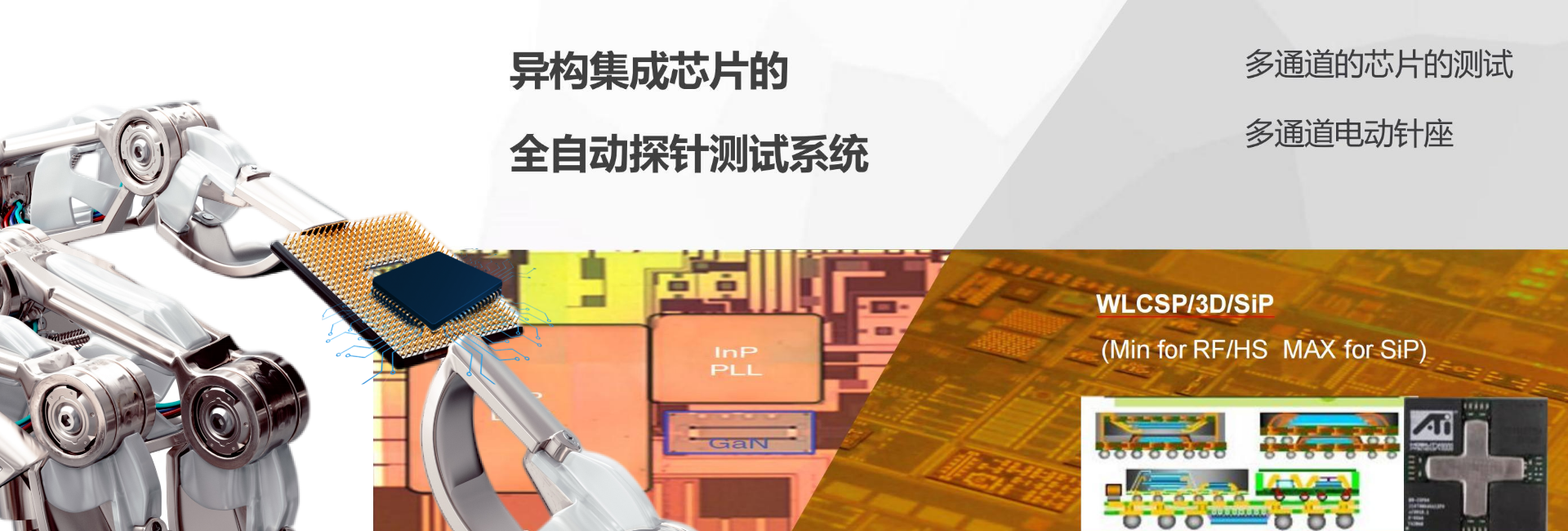

特征与优势

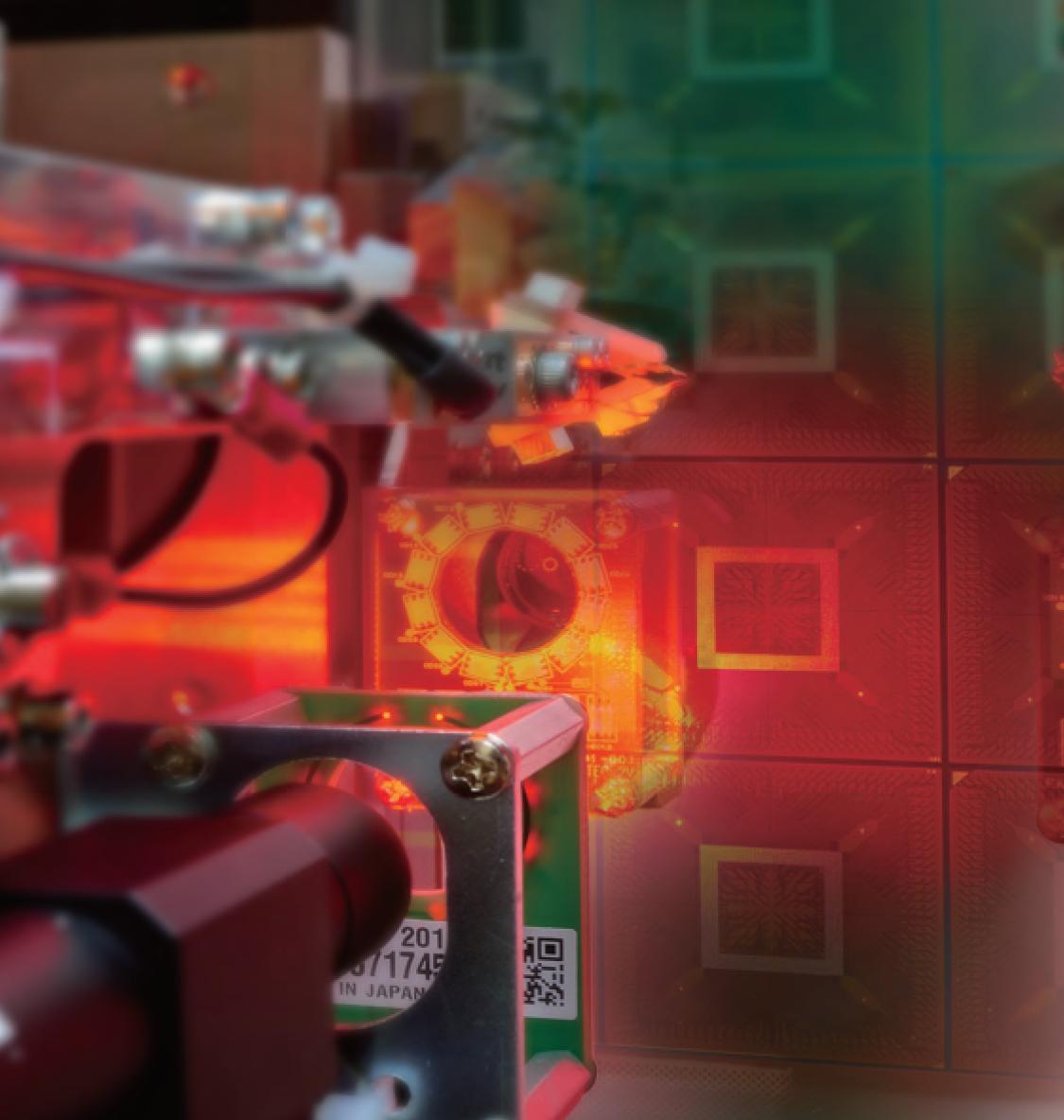

传统探针扎点与新版探针扎点

应用领域

晶圆分选

芯片分选

样品测试